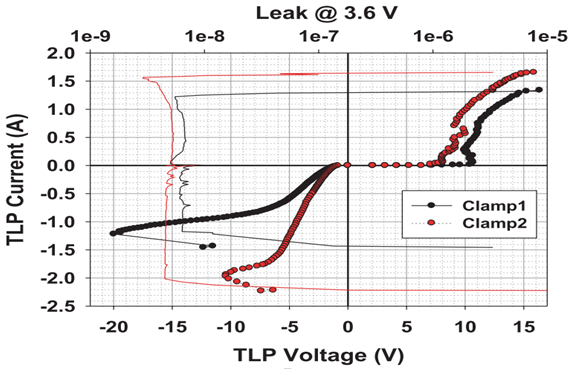

传输线脉冲(Transmission Line Pulse, TLP)

-通过电压/电流曲线分析,深入了解静电放电防护组件(ESD Protection Device)之物理特性。

-在芯片制作完成之初,即能先预测产品之静电放电的承受能力,以增加产品的研发效率。

-重视HBM ESD pulse所造成的IC失效模式及电性行为。

Nomal TLP

| TLP test model | TDR(Time Domain Reflection) |

|

Pulse Voltage |

Max:+/-2000V(0.1V/step) |

|

Pulse Current |

Max.40A |

|

Pulse Width |

100ns |

|

Pulse rise time |

200ps/2ns/10ns/20ns/50ns |

VF TLP

|

TLP test model |

TDR(Time Domain Reflection) |

|

Pulse Voltage |

Terminal Open: +/-1000V(0.1V/step) 50Ω load:+/-500V(0.2V/step) |

|

Pulse Current |

Short:Max.20A, 50Ω load:Max. 10A |

|

Pulse Width |

1ns/2ns/3ns |

|

Pulse rise time |

200ps/2ns/10ns/20ns/50ns |

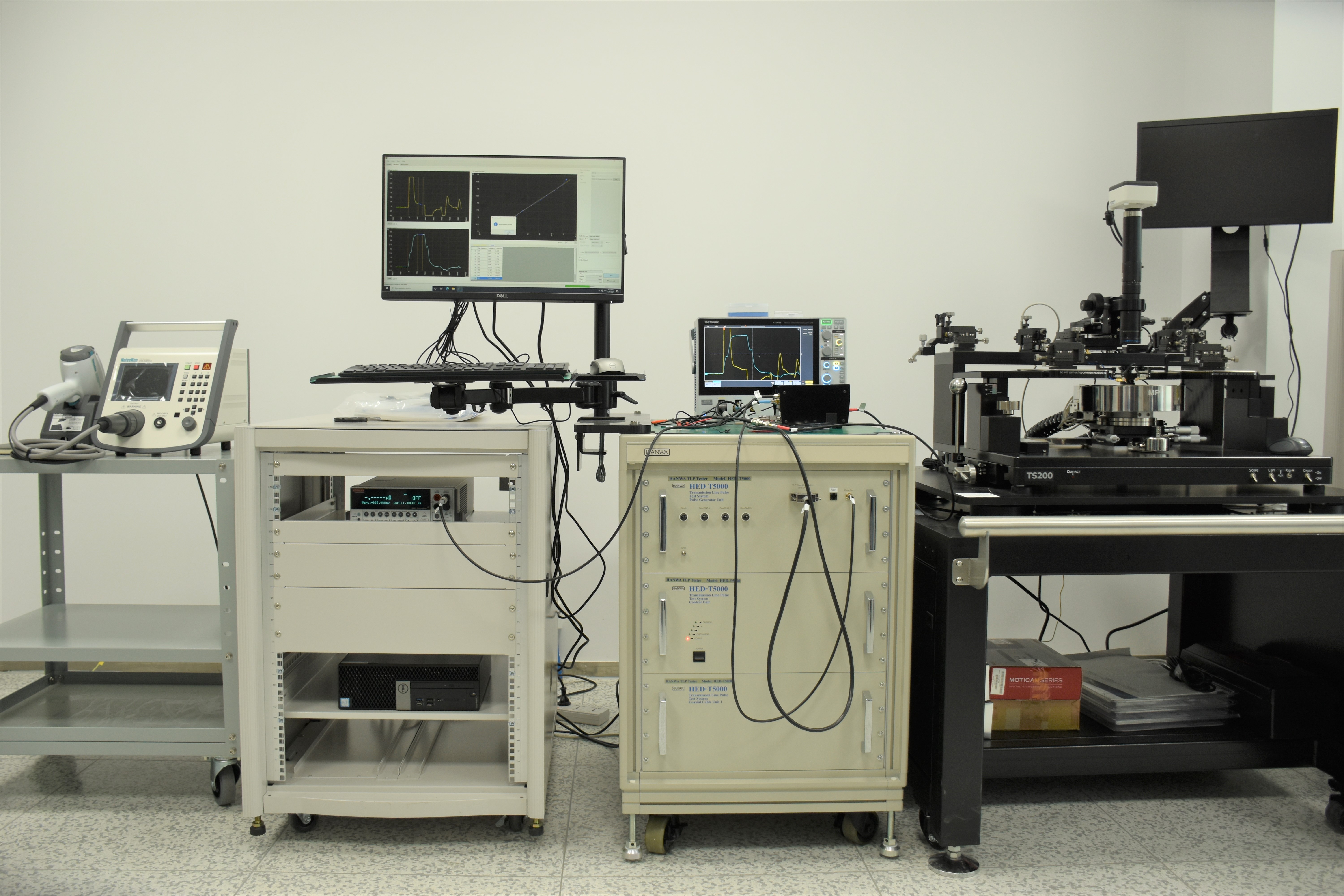

TLP测试系统